Wireless Temperature Data Logger is targeted for meat industry.

Offering 2-way communications, splash-proof RFOT is suited for smoke houses, ovens, and other cooking processes up to 212Ã-

Read More »Digi Extends ConnectCore i.MX Product Family and Freescale Collaboration with New iDigi-Enabled Wireless Module

Wireless module with Freescale processor and iDigi cloud computing service ideal for developing wireless multimedia devices MINNETONKA, Minn. - Digi International (NASDAQ: DGII) today introduced the ConnectCore(TM) Wi-i.MX53, the second in a series of core processors based on the Freescale Semiconductor i.MX processor family. The new solutions-on-module enables wired and wireless networking of...

Read More »

Camera Engine SoC allows mobile phones to output full-HD video.

Model CE151 SoC allows mobile phones to output both full HD 1080p video stream and still image data up to 13 megapixels. Noise-reduction function minimizes distortion caused by lenses, and SpeedTags(TM) technology enables users to instantly capture multiple images without any shutter lag. Image stabilizing and optical compensation features are also included. Camera Engine Software Platform is...

Read More »

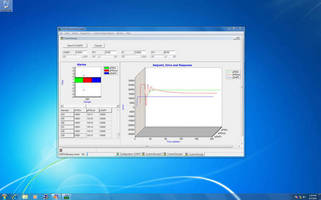

DAPtools 5.0 Supports 64-Bit Windows Systems Provides an Easy Transition for DAP and xDAP Systems

Bellevue, WA, April 8, 2010 - Data acquisition and control systems from Microstar Laboratories, Inc. can now run in 64-bit Windows systems, including Windows 7, thanks to the latest version 5.0 release of the DAPtools software packages. All Data Acquisition Processor (DAP) boards and xDAP systems use DAPtools. There are three editions of the DAPtools 5.0 packages - Basic, Standard, and...

Read More »

Everything You Need to Know About E-Textiles

This ebook provides an in-depth overview into everything you need to know about E-Textiles.

Read More »

Saelig Introduces Affordable Professional Video Processing

Pittsford, NY: HQView range of Image Scalers offers compact, affordable, high performance HDMI/DVI/Component /VGA analog to HDMI/DVI with powerful real-time image processing such as geometry correction for off-axis projection, pin/barrel, image rotation and artifact reduction. Many consumers are deeply disappointed with HD display installations when some of the content comes from lower quality...

Read More »Configurable I/O Chip has integrated return loss network.

PowerWiseÃ-® LMH0387, supplied in 48-pin CSP, provides flexibility to program BNC interface connectors as inputs (equalizer) or outputs (cable driver). Designed for SDI broadcast video equipment, chip targets 3G/HD/SD video capture and editing cards that have limited number of coax BNC connectors as well as processing and distribution equipment that support various I/O configurations. It...

Read More »Cable STB Chipset integrates uDTA support.

Featuring universal Digital Transport Adapter (uDTA) support, CX24482 speeds deployment of ADC boxes while providing universal support for multiple security systems and encryption of digital content. Cable STB IC, fully certified by Cisco and CCAD, will help cable industry transition cable network from analog to digital services. It offers DVB-compliant transport stream process with MPEG2 video...

Read More »

Floating Point DSPs (32-Bit) boost portable device functionality.

SHARC 2148x Series offers 400 MHz performance and up to 5 Mb on-chip memory, while SHARC 2147x Series, which measures 12 x 12 mm, offers 266 MHz performance, same memory, and 363 mW power (typ) power consumption. Memory usage for both series is optimized via Variable Instruction Set Architecture support, and dedicated hardware accelerators with independent compute units and DMA memory mapping...

Read More »

Automatic Video Optimizer stabilizes live and recorded video.

Suited for improving unsteady video for security and surveillance applications, IVS-200 optimizes any video source, from live feeds to DVDs and VCR tapes. With ability to stabilize shaky video in real time during capture, it corrects vertical and horizontal shaking, as well as rotation and diagonal shaking. Offering plug-and-play operation, compact unit includes analog composite I/0, correction...

Read More »

Dielectric Deposition System is designed for 3D chip packaging.

Applied ProducerÃ-® InVia(TM) dielectric deposition system uses CVD process to deposit uniform, thick oxide films in greater than 10:1 high aspect ratio (HAR) through-silicon via (TSV) structures. Process also enables electrical isolation of TSV to ensure reliable performance. For 3D packaging schemes, it electrically connects chips that are vertically stacked to boost speed and lower power...

Read More »

Krueger Sentry Gauge Announces the Release of Two New Chemical Sight Gauge Models Designed for Aggressive Liquid Storage Monitoring

Krueger Sentry Gauge, a leader in chemical sight gauges, now offers the ultimate in aggressive liquid storage monitoring devices. From sulfuric and hydrochloric acid to bleach, and acetone, our products are designed with robust features that deliver a long and trouble-free service life. See our video to learn all about this new and innovative line of sight gauges.

Read More »