SEAKR Is Building RF Processors for Saturn Satellite Networks' Small GEO Satellites 'NationSat'

Centennial, Colo., July 16, 2019 /PRNewswire/ -- SEAKR®Engineering, Inc. (SEAKR) is pleased to announce it is using next generation technologies to build digital RF processors for Saturn Satellite Networks' (Saturn) small GEO satellite known as NationSat. Saturn is a company founded by space industry veterans focused on building small geostationary satellites, and is building its first...

Read More »

Multiprocessor drives data-intensive DSP application performance.

Rugged 6U OpenVPX multiprocessor, IPN252, delivers up to 1.4 TeraflopsÃ- throughput and supports AXIS Advanced Multiprocessor Integrated Software environment. IntelÃ-® CoreÃ-® i7 CPU and 640-core NVIDIAÃ-® Maxwell GPU are connected viaÃ- 16-lane PCIeÃ-® Gen 3 switch, which also providesÃ- 16-lane PCIe Gen 3 port to VPX expansion plane, and 8-lane PCIe Gen 3 port...

Read More »ARM-Based 64-Bit SOCs combine processing power and security.

With 1–24 full custom, 64-bit ARM v8.1 cores, OCTEON TX™ CN80XX/CN81XX/CN82XX/CN83XX address control plane and data plane applications in networking, security, and storage. Operation supports 500 Mbps to 50 Gbps of Layer 3 forwarding, and features include up to two 32-/64-bit DDR3/DDR4 controllers with ECC, with up to 2,400 MTS; integrated compression engines with up to 40 Gbps; and IO...

Read More »

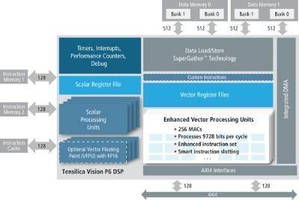

Vision DSP targets embedded neural network applications.

Based on Cadence Tensilica XtensaÃ-® architecture, CadenceÃ-® TensilicaÃ-® Vision P6 combines flexible hardware choices with library of vision/imaging DSP functions and applications. Device quadruples multiply-accumulate (MAC) performance compared to previous generation, and utilizes 8- and 16-bit arithmetic to optimize key vision functions such as convolution, FIR filters, and matrix...

Read More »

Understanding Lights Out Manufacturing

This white paper gives an overview of understanding lights out manufacturing.

Read More »Image Generator supports commercial airline pilot training.

Housed in single chassis, IndependenceÃ-® IDX 80 is designed and optimized for simulation applications requiring 2–8 separate display devices. System is powered by Intel's 6-core Xeon CPUs and NVIDIA's Quadro M-series GPUs. It includes MANTISÃ-® software for real-time visual simulation as well as GeoScapeSEÃ-® World-Wide Database. IDX 80 is suited for variety of applications...

Read More »

XMC Graphics Board serves safety-critical applications.

Available with AMD/CoreAVI Radeon E8860 Adelaar GPU, VITA 42-compliant XMCGA8 targets those who need to deliver safety-critical applications certified to DO-178 and DO-254. Air- or conduction-cooled unit can provide up toÃ- 4 DVI outputs at resolutions up to 1,920 x 1,200 at 60Hz and up to 2 VESA VGA outputs at same resolutions. With minimized TDP (thermal design power), design suits such...

Read More »

Dual-Picture Video Processor suits automotive display panels.

Combining 10-bit AD converter, multi-color decoder to accommodate all major video formats, and power-supply voltage of 1.2 V/3.3 V, Model TC90195XBG supports high-resolution widescreen displays up to 1920 x 720 pixels. Processor features 2-picture composition mode and picture-separation mode with internal frame memory. Device can simultaneously output 2 digital video signals to 2 panels, with...

Read More »SMIC Successfully Produces Qualcomm Snapdragon 410 Processor in 28nm Process

SHANGHAIÃ- – Semiconductor Manufacturing International Corporation (SMIC; NYSE: SMI; SEHK: 981) and Qualcomm Incorporated (NASDAQ: QCOM) today announced that its subsidiary, Qualcomm Technologies, Inc., and SMIC have achieved a major milestone in fabrication of 28nm QualcommÃ-® Snapdragon™ 410 processors. This milestone comes six months after SMIC and Qualcomm Technologies announced...

Read More »Diebold and Banque Internationale a Luxembourg Integrate Mobile and ATM Channels to Offer Cardless Cash Withdrawal

LUXEMBOURG - To increase security, convenience and customer satisfaction at the self-service channel, Banque Internationale a Luxembourg (BIL) has partnered with Diebold, Incorporated (NYSE: DBD) to launch a cardless transaction solution that enables end-users to remotely program and withdraw cash via a smartphone from any of the more than 100 ATMs in BIL's network. The solution provides a...

Read More »VadaTech Selected for Airborne RADAR Signal Processing and Data Recording Application

A military prime contractor in the USA has chosen MicroTCA for its airborne RADAR application. The system combines the functionality of A/D D/A Conversion, data processing, and storage in two rugged 1U rackmount systems. Both the transceiver system and the storage system utilize the same rugged chassis, but with vastly different payloads. The customer required a high-performance, compact, rugged...

Read More »

Precision Fabricating with Over 40 Years of Experience

Quality Sheet Metal specializes in delivering precision, value, and customer service. With a client base that spans many diverse industries and a reputation for excellence that goes back over four decades, our clients know that we can provide the optimal combination of value and flexibility regardless of the challenge. See our video to learn what we can do for you. Through investments in state-of-the-art design, manufacturing, and quality control systems, Quality Sheet Metal remains focused on maintaining a high standard of quality, customer service, and competitive pricing. With an emphasis on customer satisfaction, Quality Sheet Metal is dedicated to establishing long-term partnerships, similar to the ones they currently have with their valued clients. If you're looking for a new partner with extensive capabilities in sheet metal fabricating and finishing, look no further.

Read More »