Cadence Design Systems, Inc.

San Jose, CA 95134

Share:

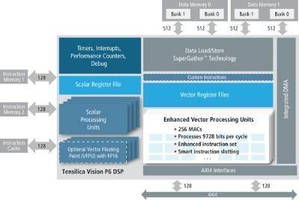

Vision DSP targets embedded neural network applications.

Based on Cadence Tensilica XtensaÃ-® architecture, CadenceÃ-® TensilicaÃ-® Vision P6 combines flexible hardware choices with library of vision/imaging DSP functions and applications. Device quadruples multiply-accumulate (MAC) performance compared to previous generation, and utilizes 8- and 16-bit arithmetic to optimize key vision functions such as convolution, FIR filters, and matrix...

Read More »SoC Verifier improves productivity and end product quality.

Intended for use-case, scenario-based software driven system-on-chip (SoC) verification, CadenceÃ-® Perspec™ System Verifier reduces complex test development to days while allowing design teams to reproduce, find, and fix complex bugs. Graphical specification of system-level verification scenarios and definition of SoC topology and actions automates system-level, coverage-driven test...

Read More »Cadence DDR4 PHY IP Achieves 2667 Mbps Performance - Fastest in the Industry

Highlights: - 2667 Mbps performance provides higher bandwidth - Reduced power for low-cost computing - Greater reliability and improved stacking capabilities SAN JOSE, Calif.Ã- – Cadence Design Systems, Inc. (NASDAQ: CDNS), a leader in global electronic design innovation, today announced that it has achieved 2667 Mbps performance on its DDR4 PHY Intellectual Property (IP) at 28nm, the...

Read More »DesignCon 2014: Get a Sneak Peak of Sigrity 16.63 at Cadence Booth #507

SAN JOSE, Calif.Ã- — Cadence Design Systems, Inc. (NASDAQ:CDNS) plans to showcase its AllegroÃ-® SigrityÃ-® solutions for signal integrity and power integrity at DesignCon 2014. Visitors will be the first to see features released in CadenceÃ-® Sigrity 16.63, including new technology supporting analysis and compliance checking of DDR4 interfaces. WHEN: Tuesday, January 28,...

Read More »Cadence C-to-Silicon Compiler Helps Renesas Realize Quick HEVC IP Development

SAN JOSE, Calif. - Cadence Design Systems, Inc. (NASDAQ: CDNS), a leader in global electronic design innovation, today announced that Renesas Electronics Corporation shortened its design and verification time by 70 percent by utilizing CadenceÃ-® C-to-Silicon Compiler to develop High Efficiency Video Coding (HEVC) intellectual property (IP), targeting consumer 4K video devices. This enabled...

Read More »EDA Software accelerates SoC verification closure.

For IP block-to-chip verification, Incisive v13.2 includes Trident engine that optimizes formal analysis, and constraint engine that speeds Universal Verification Methodology and SystemVerilog testbench simulation. IEEE 1647 e unit testing without simulation cuts debug time for testbench code. For SoC verification, program supports x-propagation to speed SoC reset and low-power simulations....

Read More »IC Design Software uses hierarchical design capabilities.

Cadence First Encounter Ultra provides virtual prototyping, physical synthesis, and full-chip hierarchical floor planning and placement. Cadence SoC Encounter front-to-back hierarchical IC implementation provides solutions for large-scale system-on-a-chip (SoC) design with 30-million gate synthesis and place-and-route capability. SoC Encounter partitions chips into smaller blocks to be designed...

Read More »Software Package assures full design verification.

NC-Sim Plus package includes NC-Sim mixed language simulator, which handles ASIC, SoC, and FPGA designs, and Verification Cockpit functional verification tool. It also includes TestBuilder open-source test bench development tool, which is based on C++ language, and includes C++ class libraries with transaction models and functions. Software package with BuildGates(R) synthesis tools is suitable...

Read More »Design System provides hierarchical access to parameters.

SPW 4.8 Signal Processing Worksystem block diagram design solution allows hardware, software, and RF engineers to collaborate on projects. Links with other tools include integrations with Xilinx Coregen solution, with analog design flow that supports Cadence(R) AMS Designer, and with SystemC 2.0. SPW 4.8 users can enter and simulate designs consisting of various types of models including C, C++,...

Read More »

Vision DSP targets embedded neural network applications.

Based on Cadence Tensilica XtensaÃ-® architecture, CadenceÃ-® TensilicaÃ-® Vision P6 combines flexible hardware choices with library of vision/imaging DSP functions and applications. Device quadruples multiply-accumulate (MAC) performance compared to previous generation, and utilizes 8- and 16-bit arithmetic to optimize key vision functions such as convolution, FIR filters, and matrix...

Read More »Cadence Completes Acquisition of Rocketick Technologies

SAN JOSE, Calif. - Cadence Design Systems, Inc. (NASDAQ: CDNS) today announced that it has completed the acquisition of Rocketick Technologies, Ltd., an Israel-based pioneer and leading provider of multicore parallel simulation. The completion of this transaction strengthens Cadence's System Design Enablement strategy by delivering ultra-high-performance simulation to accelerate the development...

Read More »SoC Verifier improves productivity and end product quality.

Intended for use-case, scenario-based software driven system-on-chip (SoC) verification, CadenceÃ-® Perspec™ System Verifier reduces complex test development to days while allowing design teams to reproduce, find, and fix complex bugs. Graphical specification of system-level verification scenarios and definition of SoC topology and actions automates system-level, coverage-driven test...

Read More »Cadence DDR4 PHY IP Achieves 2667 Mbps Performance - Fastest in the Industry

Highlights: - 2667 Mbps performance provides higher bandwidth - Reduced power for low-cost computing - Greater reliability and improved stacking capabilities SAN JOSE, Calif.Ã- – Cadence Design Systems, Inc. (NASDAQ: CDNS), a leader in global electronic design innovation, today announced that it has achieved 2667 Mbps performance on its DDR4 PHY Intellectual Property (IP) at 28nm, the...

Read More »DesignCon 2014: Get a Sneak Peak of Sigrity 16.63 at Cadence Booth #507

SAN JOSE, Calif.Ã- — Cadence Design Systems, Inc. (NASDAQ:CDNS) plans to showcase its AllegroÃ-® SigrityÃ-® solutions for signal integrity and power integrity at DesignCon 2014. Visitors will be the first to see features released in CadenceÃ-® Sigrity 16.63, including new technology supporting analysis and compliance checking of DDR4 interfaces. WHEN: Tuesday, January 28,...

Read More »Cadence C-to-Silicon Compiler Helps Renesas Realize Quick HEVC IP Development

SAN JOSE, Calif. - Cadence Design Systems, Inc. (NASDAQ: CDNS), a leader in global electronic design innovation, today announced that Renesas Electronics Corporation shortened its design and verification time by 70 percent by utilizing CadenceÃ-® C-to-Silicon Compiler to develop High Efficiency Video Coding (HEVC) intellectual property (IP), targeting consumer 4K video devices. This enabled...

Read More »EDA Software accelerates SoC verification closure.

For IP block-to-chip verification, Incisive v13.2 includes Trident engine that optimizes formal analysis, and constraint engine that speeds Universal Verification Methodology and SystemVerilog testbench simulation. IEEE 1647 e unit testing without simulation cuts debug time for testbench code. For SoC verification, program supports x-propagation to speed SoC reset and low-power simulations....

Read More »IC Design Software uses hierarchical design capabilities.

Cadence First Encounter Ultra provides virtual prototyping, physical synthesis, and full-chip hierarchical floor planning and placement. Cadence SoC Encounter front-to-back hierarchical IC implementation provides solutions for large-scale system-on-a-chip (SoC) design with 30-million gate synthesis and place-and-route capability. SoC Encounter partitions chips into smaller blocks to be designed...

Read More »Software Package assures full design verification.

NC-Sim Plus package includes NC-Sim mixed language simulator, which handles ASIC, SoC, and FPGA designs, and Verification Cockpit functional verification tool. It also includes TestBuilder open-source test bench development tool, which is based on C++ language, and includes C++ class libraries with transaction models and functions. Software package with BuildGates(R) synthesis tools is suitable...

Read More »Design System provides hierarchical access to parameters.

SPW 4.8 Signal Processing Worksystem block diagram design solution allows hardware, software, and RF engineers to collaborate on projects. Links with other tools include integrations with Xilinx Coregen solution, with analog design flow that supports Cadence(R) AMS Designer, and with SystemC 2.0. SPW 4.8 users can enter and simulate designs consisting of various types of models including C, C++,...

Read More »