Freescale Licenses Synopsys' DesignWare IP Portfolio to Accelerate SoC Designs

High-Quality, Broad Portfolio and Worldwide Technical Support Helps Freescale Speed SoC Development Time and Lower Risk MOUNTAIN VIEW, Calif. - Synopsys, Inc. (Nasdaq: SNPS), a world leader in software and IP for semiconductor design, verification and manufacturing, today announced that Freescale Semiconductor, a global leader in the design and manufacture of semiconductors for the automotive,...

Read More »ArrayComm and CEVA Demonstrate TD-LTE Base Station

Full TD-LTE PHY functionality implemented on Mindspeed SoC. NEWPORT BEACH, Calif. and MOUNTAIN VIEW, Calif. -- ArrayComm LLC and CEVA, Inc. (Nasdaq: CEVA); (LSE: CVA), today announced the successful demonstration of ArrayComm's BasePort(TM) TD-LTE base station PHY running on high performance CEVA DSP cores. The demonstration was implemented on Mindspeed's Transcede(TM) 4000 System-on-Chip and...

Read More »Application-Level Interface Core aids PCIe FPGA integration.

IP core PCIEXPAIF provides high-level interface between system buses such as AMBAÃ-® AXI4 and PCI Express (PCIe) hard macro blocks available from FPGA vendors Altera and Xilinx. In addition to extensible DMA and other functions to encode and decode Transaction Layer Packets, core includes support for 32- and 64-bit versions of open source Wishbone Bus as well as AMBAÃ-® AHB(TM), AXI(TM),...

Read More »Controller IP Core enhances chip-to-chip serial interfaces.

Providing flexibility needed to facilitate board-level design for high-speed chip-to-chip serial interfaces, Interlaken core features fully configurable SerDes lane mapping between logical and physical SerDes lanes. HiFlex architecture is included along with Interlaken-LA, In-Band and Out-of-Band flow control, multiple UI options, flexible statistics counters, and built-in interrupt structures....

Read More »

Understanding Water Hammer

DFT Inc's engineers have been working with professionals in a range of industries for decades, helping to identify and resolve the underlying causes of water hammer. In this eBook you will learn about many of these common causes, how they impact your system and some of the basic changes you can make to eliminate them. In this eBook you will learn: What causes water hammer and why it is such a persistent problem. The role design plays in reducing the risk water hammer poses to your system. DFT's professional recommendations for coping with water hammer.

Read More »Integrated 100G EFEC IP Cores optimized for FPGAs.

With respective overhead ratios of 7% and 20%, EFEC7 and EFEC20 multidimensional enhanced forward error correction (EFEC) IP cores are optimized for StratixÃ-® IV and Stratix V series FPGAs. Functionality targets service providers upgrading 10G metro networks and long-haul OTNs to 100G speeds and planning for future 400G support. Both products leverage Streaming Turbo Product Code BCH code...

Read More »SATA Device Controller IP includes CPU offloading capabilities.

Targeting 6 Gbps SSD applications, CEVA-SATA3.0 incorporates Native Command Queuing specifications for Isochronous data transfers and queue management, which in turn enables prioritized transfers of streaming audio and video data. Licensable RTP IP package is accompanied by complete set of deliverables, including comprehensive simulation environment, example C source code, and FPGA-based...

Read More »

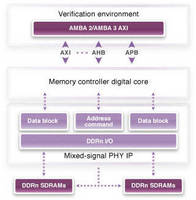

MultiPHY IP supports 6 DDR standards.

DesignWare(TM) DDR multiPHY supports range of DDR SDRAM standards - LPDDR2, LPDDR/Mobile DDR, DDR3, DDR3L (1.35 V), DDR3U (1.2x V), DDR2 - in single PHY. This lets designers target different DDR types for single chip through software control, promoting flexible integration into various applications. Supporting data rates from 0-1,066 Mbps, product offers DFI 2.1-compliant interface to memory...

Read More »Microcontroller IP Model Libraries support JTAG/Boundary Scan.

Structured modularly as intelligent IP, VarioTAPÃ-® models for Microchip PIC32MX microcontrollers with MIPS(TM) Core enable complete fusion of boundary scan test and JTAG emulation. By employing this technology, on-chip Flash of PIC32MX types can be in-system programmed. Both embedded Flash and external Flash are supported. In addition, VarioTAPÃ-® supports interlaced bus emulation tests...

Read More »Controller IP Cores target next-generation chip designs.

Based on preliminary version of PCI ExpressÃ-® 3.0 specification, Databahn(TM) Controller IP Cores accelerate overall deployment of PCIe 3.0 technology into storage and networking systems. Preliminary PCIe 3.0 specification increases PCIe 2.0 interconnect bandwidth from 5 GT/s to 8 GT/s. Cores support TLP Prefix, Atomic Operations, Resizable BARS, and Alternative Routing-ID, as well as...

Read More »HDMI 1.3 Receiver Interface enhances digital home solutions.

Based on 90 nm technology, 45 nm HDMI 1.3 receiver IP solution is comprised of HDMI RX controller and HDMI RX PHY. Controller features video interface flexibility, supporting all CEA-861D video formats, and also supports True Color and Deep Color modes and several video pixel encodings as well as Gamut Metadata. Capable of supporting cables up to 20 m, HDMI 1.3 RX PHY features automatic adaptive...

Read More »

Paratherm™ HR Heat Transfer Fluid: Higher Temperature Stability Leads to Longer Fluid Life

For the ultimate in heat transfer fluid performance, Paratherm offers HR Heat Transfer Fluid that is engineered specifically for closed loop liquid phase heating. When it comes to characteristics such as thermal stability and fluid degradation, Paratherm HR leads the industry in value and performance. See our video to learn how Paratherm is raising the bar for heat transfer fluids.

Read More »