PLL/Synthesizer operates from 3,900-4,300 MHz.

Press Release Summary:

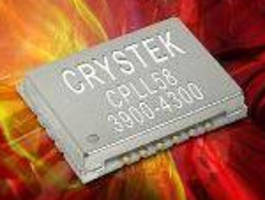

With typical step size of 2,500 KHz, model CPLL58-3900-4300 wraps VCO around PLL in 0.582 x 0.8 x 0.15 in. SMD package and requires only external frequency reference and supply voltages. It is programmed using standard 3-line interface - data, clock, and load enable - and exhibits typ phase noise of -95 dBc/Hz @ 10 kHz offset with min output power of 3 dBm. VCO voltage is 5 Vdc, PLL voltage is 3 Vdc, and second harmonic suppression is -15 dBc typ.

Original Press Release:

New 3900-4300 MHz PLL/Synthesizer

Fort Myers, FL - September 11, 2009 - Crystek's CPLL58-3900-4300 PLL/Synthesizer operates from 3900 MHz to 4300 MHz with a typical Step Size of 2500 KHz. Engineered and manufactured in the USA, the model CPLL58-3900-4300 is housed in a compact 0.582-in. x 0.8-in. x 0.15-in. SMD package, which saves board space.

Crystek's PLL/Synthesizer construction essentially wraps a VCO around a PLL in a package that's only marginally larger than a VCO on its own, and significantly smaller than separate VCO/PLL modules. The CPLL58-3900-4300 is a complete PLL/Synthesizer needing only an external frequency reference and supply voltages for the internal PLL (phase lock loop) and VCO (voltage controlled oscillator). The Crystek CPLL58-3900-4300 is programmed using a standard three line interface (Data, Clock and Load Enable).

Typical phase noise for the CPLL58-3900-4300 is -95 dBc/Hz at 10 KHz offset with minimum output power of 3 dBm. VCO voltage is 5 Vdc; PLL voltage is 3 Vdc. Second harmonic suppression is -15 dBc typical.

The CPLL58-3900-4300 is ideal for use in telecommunications, computers, radio equipment, base stations and other electronic applications. For pricing details, contact Crystek Corporation.